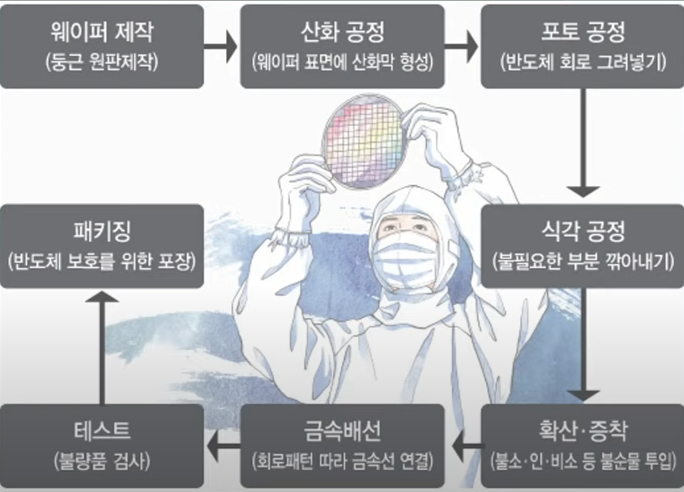

반도체 8대 공정

1. 웨이퍼 제작 (둥근 원판제작)

2. 산화 공정 (웨이퍼 표면에 산화막 형성)

3. 포토 공정 (반도체 회로 그려넣기)

4. 식각 공정 (불필요한 부분 깎아내기)

5. 확산,증착 (불소, 인, 비소 등 불순물 투입)

6. 금속배선 (회로패턴 따라 금속선 연결)

7. 테스트 (불량품 검사)

8. 패키징 (반도체 보호를 위한 포장)

반도체 8대 공정

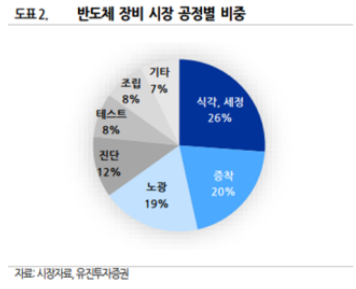

반도체 공정별 비중

반도체 공정별 비중

식각, 세정이 가장 높은 26%, 증착이 20%, 노광이 19% 순으로 이뤄짐.

순서대로 공부를 해보자.

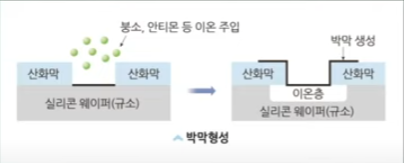

증착공정= 박막공정

- 웨이퍼 위의 얇은 두께의 박막을 입히는 과정

쉽게 이해하면

- 회로가 지나가는 길을 만드는 과정 + 반도체 성능을 높이기 위해 여러 층을 겹쳐 만들때 회로가 층층이

쌓일 수 있도록 절연막을 형성하는 과정

반도체에는 수많은 회로가 있는데 수많은 회로가 가까워지면 안됨. 가까워지면 서로 영향받아서 불량이 나서

반도체 회로 사이사이를 막을 수 있는 전기가 통하지 않게하는 절연막을 만들어줘야함.

그 과정을 이 확산, 증착공정을 통해 만듦. 아래층의 회로, 위층의 회로 방해 받지 않으려면

아래층의 회로에 절연막을 덮고 위층 회로를 만들어야 방해 안받음.

이렇게 절연막 형성하는걸 박막 형성이라함.

반도체는 나노공정을 통해 미세한 공정을 진행 하는데

박막도 나노미터에서 마이크로 단위 아주 얇은 막

반도체같은 아주 미세한 공정할때 막도 아주얇은 막을 써야해서

박막 공정이라고 함.

이 박막을 씌우는 공정은 매우 고난이도 기술력이 필요한 공정.

- 얼마나 얇고, 균일하게 입히는게 중요한 공정

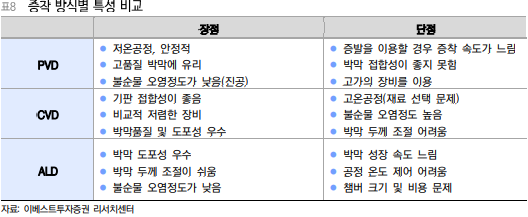

증착의 방법은 크게 두가지로 나뉨.

1. 물리적 증기증착 (PVD) : 특정 물질에 직접 에너지를 보내 증착

- 1.1 Thermal Evaporation

- 1.2 E-beam Evaporation

- 1.3 Sputtering

2. 화학적 증기증착 (CVD) : 반응 가스들의 반응으로 물질을 증착

- 2.1 APCVD

- 2.2 LPCVD

- 2.3 PECVD

- 2.4 HDPCVD

- 2.5 ALCVD (ALD)

PVD (물리적 증기증착)

- 주로 터치스크린패널, 디스플레이에 사용 (미세할수록 크랙이 생기기 때문)

- 고체->기체-> 고체 (단순한 물리적 상태 변화)

- 주로 증발법보다는 플라즈마를 이용한 Sputtering 증착을 이용하는데, 금속막을 증착할 떄 주료 사용함.

상대적으로 막질이 우수하고, CVD보다 화학물질 사용량이 적고 진공상태에서 진행하기 때문에 불순물 오염정도가 낮다는 장점이 있음.

PVD: Sputtering

(Physical Vapor Depostion, 물리적 기상 증착)

- 증착할 물질에 직접 에너지를 인가하여 증착

- CVD에 비해 공정의 증착 속도가 느리지만 박막의 품질 우수

- CVD는 전구체라는 물질을 통해서 증착하는 반면, PVD는

전구체 필요 없음.

PVD 주요방법

1. 증발법 (Evaporation): 도가니 안에 담긴 물질을 끓여 기화시키는 방법

2. 스퍼터링 (Sputtering): 양이온을 타겟 물질에 입사시켜 떨어진 타겟 물질을 웨이퍼에 증착시키는 방식

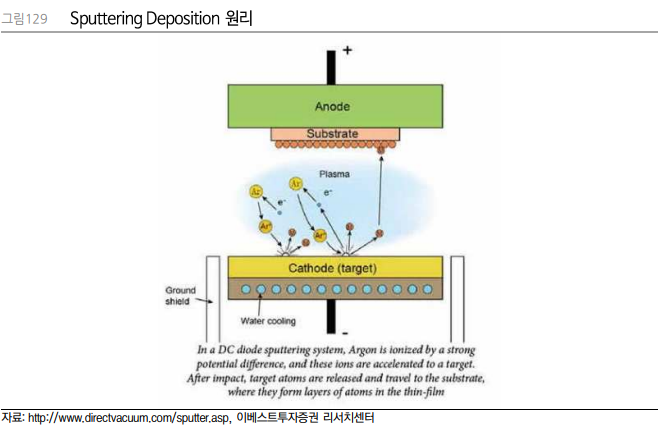

기본적으로 챔버 안에 증착 기판(Sub)에는 Anode + 극을 연결하고 Target 기판은 Cathode - 극을 연결함.

이후 비활성기체인 Ar 기체를 넣은 후 강한 전압을 -극에 가해주게 될 경우, 전자가 방출되면서 + 극으로

가속화되면서 Ar 원자와 충돌하게 됨.

이렇게 자유전자와 Ar 기체를 충돌시킬 경우 Ar + 양이온이 만들어지게 됨. (글로우 방전 현상 이용)

전자와 중성원자의 충돌에 의한 이온화 과정:

Ar (+) e- -> Ar+ (+) e- (+) e-

형성된 양이온은 음전압이 가해진 타겟 물질 기판에 충돌하게됨.

이 때 충돌된 타겟 물질 원자가 튀어나오게 되고, 운동에너지에 의해 반대편에 위치한 웨이퍼로 이동하여

증착됨.

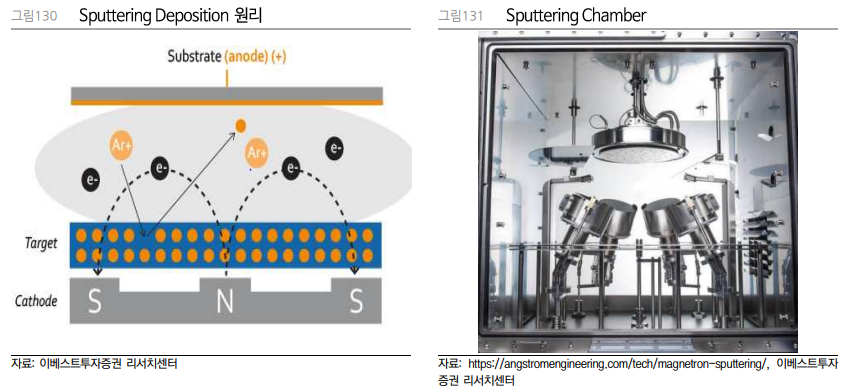

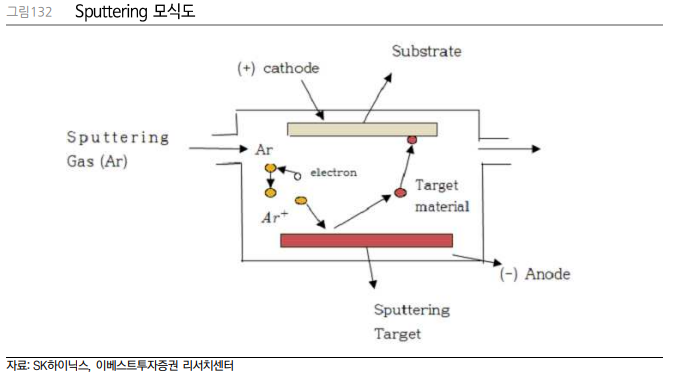

기존 Sputtering 공법은 증착 속도가 느리고, 글로우 방전 현상을 이용하기 떄문에

많은 양의 가스가 필요함에 따라 박막의 불균일과 damage 발생요인이 크다는 단점이있었음.

그러나 Magnetron Sputtering의 도입으로 인해 증착 속도 증가시키고, 성막후 열차리 공정을

추가하게 되면서 불균일과 damage를 감소시키게 되었음. 기본적으로 Sputtering 공법은

박막의 응착력이나 균일도, Step Coverage, 다양한 시료를 이용 가능한 점 등이 뛰어난 편에 속함.

CVD (화학적 증기증착)

- 주로 반도체에 사용

- 저기압, 고밀도, 얇은막으로 갈수록 좋은 기술

- 웨이퍼 표면에서 가스가 반응하여 원래의 기체 원소와 다른 화학적 조성 갖게 됨.

- 가장 사용량이 많은 증착 방식.

- 가스의 화학적 반응을 이용하기 때문에 방식이 간단하고 저렴.

- 화학반응식을 이용하기 때문에 선택비가 높은 장점 있음.

- 화학 가스를 사용하기 떄문에 불순물 오염 정도가 높은 단점 있음.

- 핵심 제어요소: 진공압력, 온도, 화학적 원소

- 최대한 얇게, 밀도는 높이는게 기술

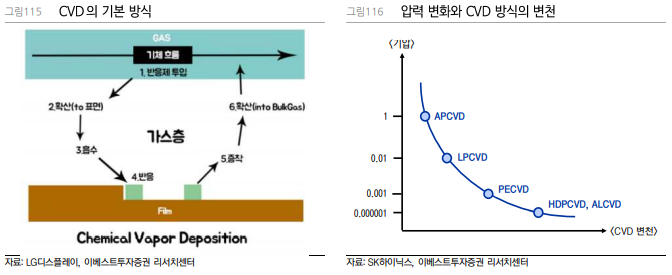

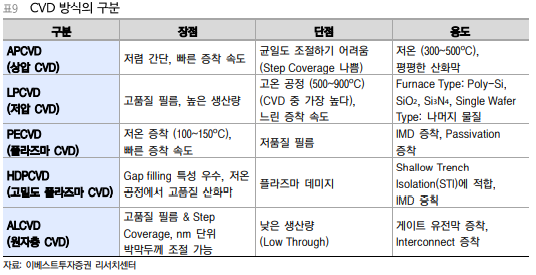

- CVD의 구분 기준은 압력 기준. 프로세스 챔버 내에 압력을 낮출수록 더 정밀하고 균일하며, 단차피복성이 높고 두께 균일성이 높은 막이 형성됨. 저압 상태에서는 공정시간이 길어져, 반응속도 떨어뜨리지 않기 위해 웨이퍼 온도를 높여 야하는 방식으로 바껴옴.

- 웨이퍼 열온도를 높일수록 막에 주는 스트레스가 커지게 되는 등 여러 단점들이 생겨남.

- 해결 방식으로 플라즈마 에너지를 보충하여 증착시키는 PECVD 방식이 등장함.

- 하지만 PECVD방식은 기체인 radical (염소나 불소 원자와 같은 반응성이 강한 물질을 사용)을 사용하기 떄문에

- 막질 상태가 다소 좋지 못하는 단점 존재. 이를 해결하기 위해 플라즈마 식각과 증착을 함께 이용하여 gap fill 능력을 향상시킨 HDPCVD 방식이 점점 빠르게 증가하게 됨.

그냥 뒤로 갈수록 기술이 좋아진다. 저기압, 고밀도 , 얇은막

APCVD-> LPCVD-> PECVD-> HDPCVC, ALCVD 이 순으로 개발 된것으로 이해

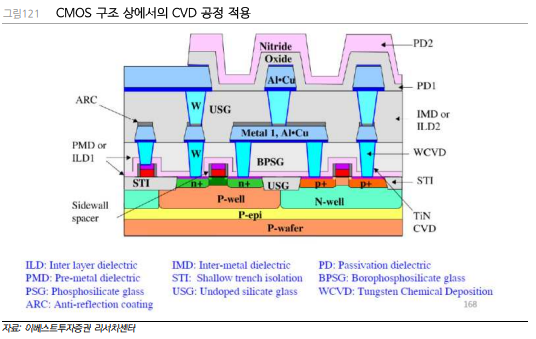

ALD 가 현재 가장 고도화 된 기술이나 그렇다고 CVD방식이 전부 ALD로 가는 것은 아님.

극 미세화된 부문 (DRAM Capacitor, Gate Oxide(HKMG)) 등은 ALD이지만

Passivation, STI, IMD, Gate 층은 여전히 CVD 방식이 주로 사용.

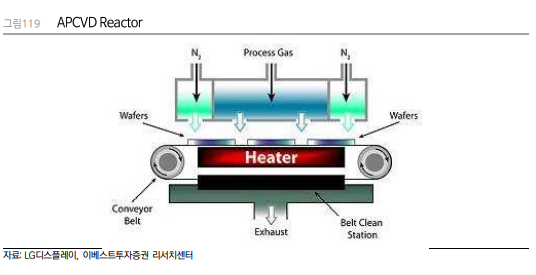

APCVD (대기압 CVD)

(Atmospheric Pressure CVD)

- CVD 공정의 초창기 공정.

- Chamber를 가열하지 않고 챔버 외부의 RF 인덕션 코일을 가열하여 웨이퍼에 열 전달하는 방식

- 대기압의 특성으로 인해 미세화 난이도가 높아지고 메탈층의 집적도 높아지면서 APCVD 균일도 한계 발생.

- 8인치 웨이퍼에서 주로 사용되었고 12인치 웨이퍼가 주로 사용되는 현재에는 거의 적용하지 않음.

저압 상태가 될수록 좋은 품질의 막질과 얇은 막을 만들기 유리해지기 때문에, APCVD 기술은

LPCVD (Low Pressure CVD) 방식으로 바뀌게됨.

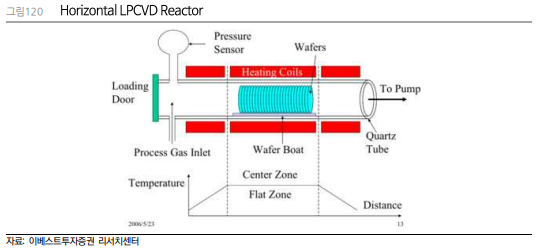

LPCVD (저기압 CVD)

- LPCVD는 APCVD 대비 챔버내 기압을 1/100 수준으로 낮추게 됨.

- 이러한 저압 방식이 진행되면서 진공도가 높아질수록 가스 분자들끼리의 충돌이 적어지고,

- 이는 기체 확산속도의 증가로 이어지면서 APCVD에 비해 더 정밀하고 균일한 필름 만들 수 있게 됨.

- 전체적으로 트렌치나 gap 또는 hole의 단차 피복성 또한 증가하는 등의 여러 장점이 생겨나게 됨.

- 문제는 저압상태로 갈수록 공정시간이 길어지기 때문에 이를 해결하기 위해서

- 웨이퍼 온도를 높이는 과정이 필요했음.

- 이에 따라 LPCVD는 APCVD에 비해 온도가 2배 가량 증가하게 됨.

(여기까지 이해 안가면 쉽게 이해하자.

APCVD는 반도체 공정기술이 정밀해지면서 균일도에 한계가 생겨서

해결하기 위해 저압으로 균일도를 높인 LPCVD사용. 그러자 속도가 느려짐.

속도가 느려져서 웨이퍼 온도를 올려야했는데 올리면 막들에 문제생겼음.)

온도 2배를 증가시켰는데 반도체 집적도가 증가하면서 온도증가에 영향을 받는 막들이 증가하게 되었음.

Poly Gate, Gate Oxide 절연막과 같은 하부층에 있는 막은 LPCVD를 진행하면서 웨이퍼 온도를 높여도

하부에 녹는 막이 없지만, IMD (Inter-Metal Didlectric) 층과 같은 트랜지스터 상부층에 위치한 막의 경우에는

그 아래의 word line 이 녹아 내리는 현상이 발생함. 이에 따라 낮은 온도에서 저압상태의 장점을 누리면서

LPCVD와 유사한 효과를 낼 수 있는 PECVD 장비가 개발되게 되었음.

PECVD는 열에너지 대신 플라즈마 에너지를 보충 사용하게 되는 저온 (약 400도) 공정.

(쉽게 이해하면 열 올리니까 반도체 아래는 괜찮았는데 위에가 녹아내려서 열올리는거 대신 똑같은 효과를

내는 플라즈마에너지를 사용해서 저압상태에 낮은온도로 LPCVD 효과 낼 수 있는게 생김 그게 PECVD)

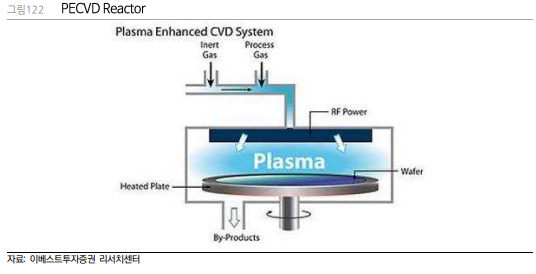

PECVD

PECVD (Plasma Enhanced CVD) 공정의 경우,

- 저온 (약 400도)에서도 가능하다는 장점을 바탕으로 가장 보편적으로 사용되는 공정

- LPCVD 공정과 가장 큰 차이점은 열에너지가 아닌 플라즈마 에너지 사용한다는 점.

- 반응시킬 기체를 주입한 상태에서 높은 전압을 수직으로 인가해줌.

- 이후 높은 전압에 의해 분자상태로 존재하는 기체가 이온으로 나눠지면서 플라즈마 상태가 되고

- 그러면 이온화된 기체들이 서로 화학 반응을 하여 원하는 물질은 기판에 고르게 쌓이고

- 나머지 이온들도 결합하여 기체로 배출되게 됨.

- PECVD는 열에너지가 적게 소모되고 막 품질이 다소 떨어져도 괜찮은 층간 절연막 등을 형성할 때 많이 사용

ex: IMD, ILD의 일종인 Sio2 형성할 때, Passivation막 (주로 Si3N4),

PMD (Pre Metal Dielectirc): (절연층 역할) 형성할 때

(IMD (Inter Metal Dielectrics): 금속 배선의 합선 등을 방지하기 위한 절연층

ILD (Inter Later Dielectrics) : DRAM cell 및 Peri circuit과 Capactor 간의 층간 절연층)

쉽게 이해하면

IMD: 금속 간의 절연층

ILD: 각 역할을 하는 층간의 절연층)

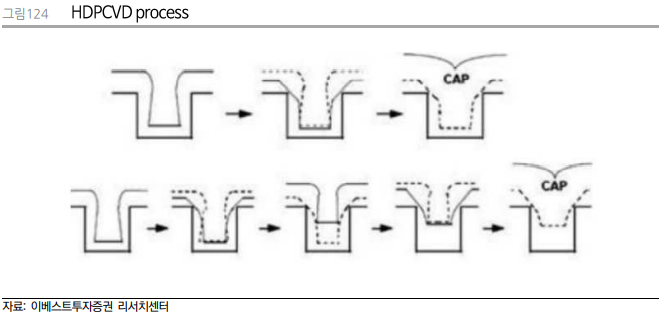

HDPCVD (고밀도 플라즈마 CVD)

(High Density Plasma CVD)

- 플라즈마 증착과 식각을 모두 이용하여 이 둘의 속도를 조절하여 Layer를 형성하는 방식

- 상대적으로 플라즈마 농도가 높아질수록 증착 속도가 빨라짐

- 동시에 플라즈마 식각을 함께 이용하기 때문에 막질의 두께가 불균일한 문제 해결 가능한게 큰 창점

- 식각으로 사이공간을 확보한 상태에서 증착이 더 쉬워지기 때문에 (Sputtering 식각 시에 Ar 이온의 직진성을

확보해주면 증착할 공간이 충분히 확보) 미세화 process 문제로 지적되는 void가 발생될 확률을 줄일 수 있음.

- 이러한 장점으로 인해 트렌치나 Gap을 채우는데 사용.

- 특히 소자 분리방식으로 사용되는 STI (Shallow Trench Isolation)을 형성하는데 사용

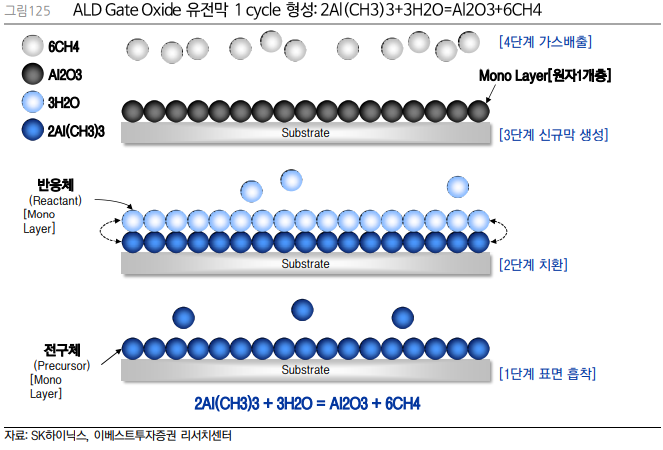

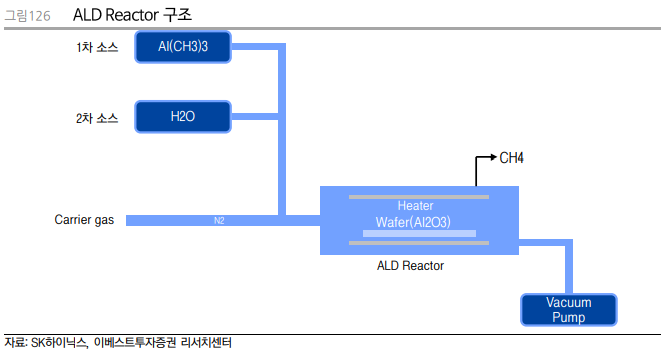

ALD

(Atomic Layer Deposition)

- 공정속도가 느리다는 치명적인 단점 있음.

- EUV 적용하며 Masking수가 확 줄어들며 사용가능하게 됨. 속도가 느려도

- EUV 장비 확대되면 가장 필요한 공정

- ALD (원자 단위 증착) 기술은 기존의 CVD와 PVD 보다 더 얇고 미세한 막의 형성이 필요해지면서 등장

- ALD는 기본적으로 프리커서(Precursor) 화학물질과 특정 반응물질 (Reactant)을 번갈아가면서 반복 주입해

- 웨이퍼 표면에서만 화학반응이 일어나도록 유도하는 공법이라고 할 수 있음.

- '자기제한적 표면처리 공법' 보유. (아무리 소스 많이 공급해도 원자층 1개 층만 쌓이는 것, 반응 표면만 반응,

나머지는 반응 일어나지 않음. 이에 따라 증착 표면 두께 관리가 용이해지고, 기술자가 컨트롤 가능함)

- 참고로 위에서 1개층 형성되는게 1 cycle

정리하면

-> 프리커서와 Reactant 를 표면 화학적 반응에 의해 원자층을 하나씩 쌓아가는 미세박막 증착 기술.

( SK트리켐이 알려주는 프리커서 (skcareersjournal.com) 프리커서 이해하려면 보면 좋음)

CVD와 비교하면

- CVD는 챔버 안의 진공 공간과 웨이퍼 표면 모두에 화학 반응이 일어나 막이 쌓임.

- ALD는 표면에서만 반응이 일어나기 때문에 막 두꼐를 절반으로 구현 가능.

- 또한 원자층 형성에 쓰이지 않은 원자는 튕겨져 나가기 때문에, 기존 박막보다 일정한 굵기로 막 형성 가능.

- CVD, PVD 는 자기제한적 표면처리공법 보유하지 못함. 즉, 소스 공급하면 두껍게 막 형성됨.

ALD 사이클

표면흡착, 치환, 신규막생성, 배출

이게 1cycle

원자 1개층을 Mono Layer (ML) 이라고 부름.

위 그림은 Gate Oxide 유전막 형성을 위해 Al203 형성을 위해 사용되는 1cycle

ALD는 주로

1. DRAM Capacitor 형성

2. DRAM 및 Logic 에서 Gate Oxide 증착

3. 3D NAND에서 칩 가장 아랫단까지 전극 역할을 하는 텅스텐

을 증착시키는 공법으로 사용 됨.

이 공정은 전부 High Aspect ratio, conformal, uniform, 초미세화 등의 수요가 증가하는 공정들.

현재 ALD 의 단점이었던 생산성 문제 또한 배치타입 ALD (웨이퍼를 한꺼번에 투입하여 처리량을 증가)나

웨이퍼를 움직이면서 박막을 진행하는 Spatial Type 공법이 개발되고 있음.

최근에는 ALD 에서 파생된 원자층을 식각에 활욯나느 원자층 식각공법 (ALE)나

원하는 웨이퍼 표면에만 원자층 증착을 하는 공법등이 연구되고 있는 상황.

그 외에 높은 공정 온도 제어를 위해 플라즈마를 사용하여 저온에서도 박막 증착이 가능한

PEALD 기술 또한 제시되고 있고

PEALD에서 플라즈마가 주는 데미지를 최소화하기 위해

RPEALD (Remote PEALD) 기술 또한 개발 되고 있음.

RPEALD의 경우, 플라즈마가 다른 공간에서 발생하여 ALD 리액터로 들어오기 떄문에

ALD 리액터에서 바로 플라즈마 반응을 일으키는 것보다 데미지를 더욱 최소화시킬 수 있음.

이온 주입 공정

- 증착공정 (박막공정)이 끝난 후에는

- 반도체가 전기적인 성질을 가지게 하는 이온 주입 공정이 필요함.

- 순수한 반도체는 규소로 되어 있어 전기가 통하지 않으나

- 불순물을 넣어줘 전류를 흐르게 하는 전도성을 갖게 되는 것.

증착 및 식각의 주요 용어공부

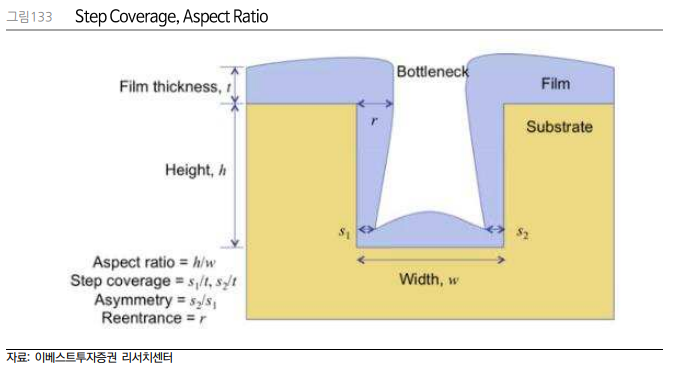

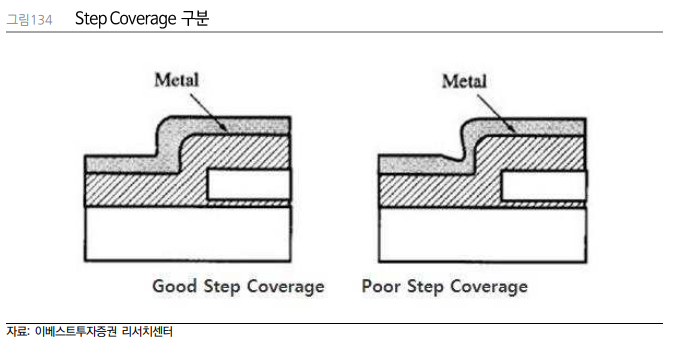

1. Step Coverage (단차 피복성) , S/C 로 표현

- 단차에서의 일정한 두께를 유지하는지 여부

- 수평방향과 수직방향간의 증착 비율의 균일도를 나타냄.

- s값과 t 값을 나눈값을 단차 피복성 측정하는데 사용

- 1에 가까울수록 단차피복성 (S/C) 가 우수하다고 판단.

- S/C 불량할 경우, 박막을 두껍게 증착하게 되었을떄 박막 사이가 비어있는 Key-Hole Effect 발생하기도함.

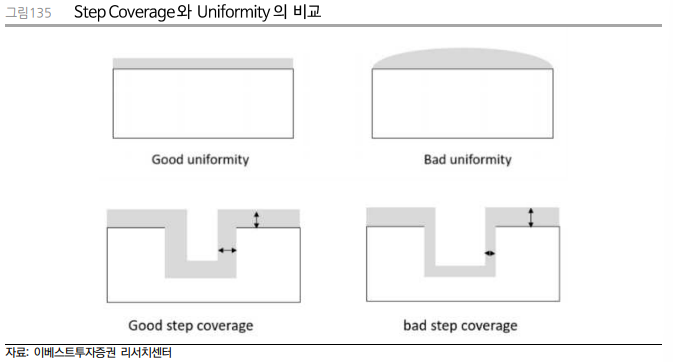

2. Uniformity (균일도)

- S/C 는 기판위의 두께와 벽면의 두께를 비교하는 반면,

- 균일도 (Uniformity)는 '일직선' 상에서의 균일한 증착 및 식각정도를 판단하는 척도

- S/C 는 주로 증착에서, Uniformity는 주로 식각 공정에서 사용되는 용어

- 좋은 Uniformity 를 가졌다 하더라도, 기판 위의 두꼐와 벽면 두께가 다르게 증착되면

좋은 S/C를 가졌다고 말할수는 없음.

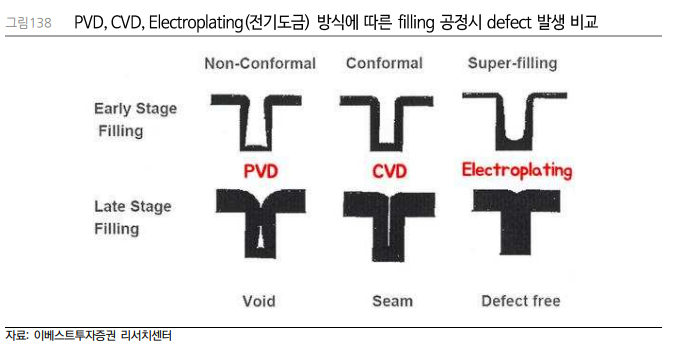

3. Void 발생 유무 (Gap Filling 능력)

- S/C가 우수한 경우에는 종횡비가 높은 패턴이라도 단차 사이를 박막으로 잘 채울 수 있으나

- S/C가 우수하지 못한 경우 단차 사이에 빈 공간이 발생하게 됨.

- 이 공간을 PVD 공정에서는 Void, CVD 공정에서는 Seam 이라 일컬음.

- 결론적으로 단차를 채우는 Filling 공정에서 S/C가 완벽한 상태 (Conformal Step Coverage:

단차피복이 1:1에 수렴)에 가까워질수록 이러한 Void와 Seam이 적어지게 됨.

증착 대표기업

- 원익 IPS (국내 증착장비 1위): PE CVD, ALD(준비중), Metal CVD (삼성향 비중 높음)

- 유진테크 : LP CVD, ALD

- 주성엔지니어링: ALD (대장), PECVD

- 테스: PE CVD (낸드, SK하이닉스 비중 높음), ACL (미세공정시 포토레지스트 두께 얇아져서 무너짐. 보완위해 하드마 스킹 (ACL과 Sion)이 필요. 이거 해주는 장비가 ACL 장비. (PECVD ACL 장비라고 함)

LPCVD

- 국내: 유진테크

- 해외: TEL (도쿄 일렉트론), AMAT (어플라이드 머트리얼즈)

PECVD

- 국내: 원익 IPS, 테스, 주성엔지니어링

- 해외:AMAT, 램리서치, TEL

싱글ALD

- 국내: 주성엔지니어링 (대장), 원익IPS, 유진테크,

- 해외: ASML (대장) , 램리서치, AMAT

배치ALD

- 국내: 유진테크 (국내 대장)

- 해외: TEL (글로벌 대장)

다음은 식각, 세정 공정 정리 해드릴게요

출처: 삼성전자, 유진투자증권, 이베스트투자증권

'반도체 공부' 카테고리의 다른 글

| 반도체 8대공정- (5,6사이)CMP공정 (0) | 2022.04.15 |

|---|---|

| 반도체 8대공정- 6. 금속, 배선공정 (0) | 2022.04.15 |

| 반도체 8대공정- 4.식각공정 (1) | 2022.04.11 |

| 반도체 8대공정- 3. 포토공정 (7) | 2022.04.08 |

| 반도체 8대공정 정리-1.웨이퍼제작, 2. 산화공정 (3) | 2022.04.06 |

댓글